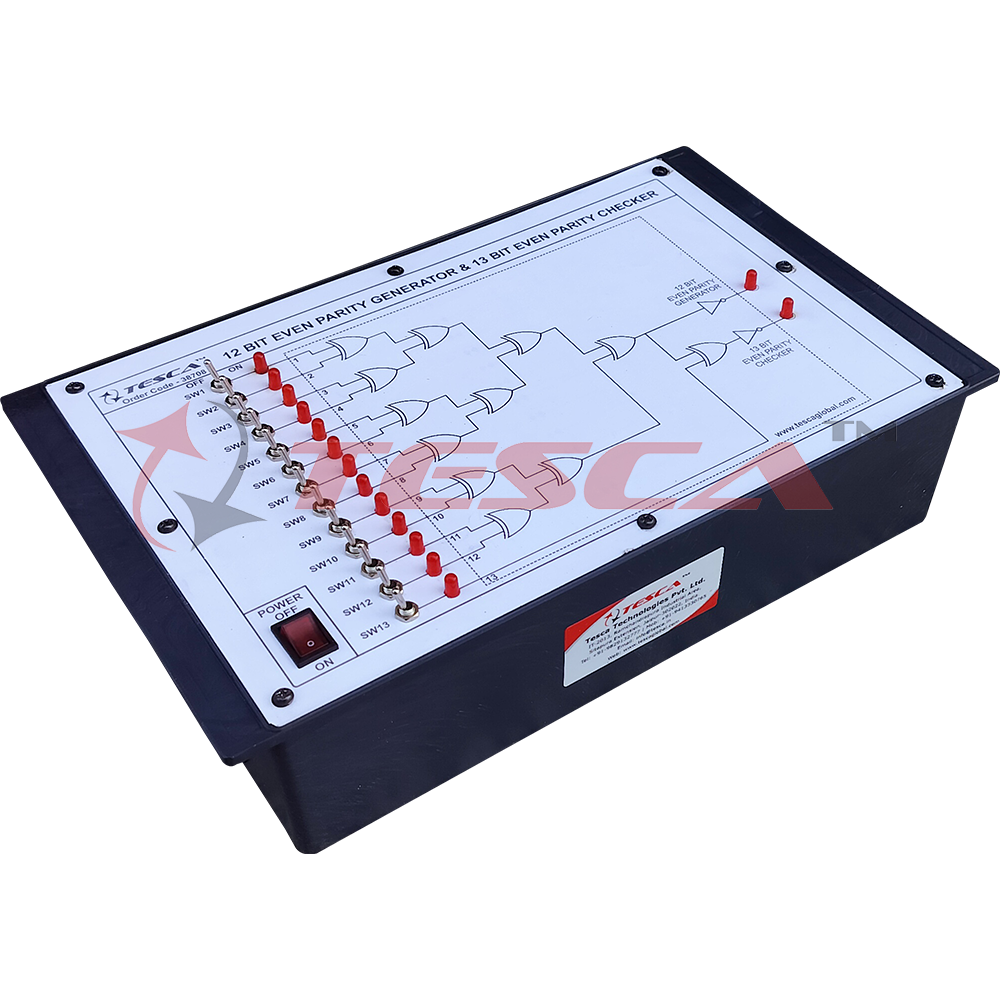

12 Bit Even Parity Generator and 13 Bit Even Parity Checker

Order Code: 38708

Category: Digital Electronics Trainers

38708 Experimental Training Board has been designed specifically for the study of Even Parity Generator and Even Parity Checker in solid state version. Even Parity Generator and Even Parity Checker play an important role in error detection. As Even P...

SPECIFICATION

38708 Experimental Training Board has been designed specifically for the study of Even Parity Generator and Even Parity Checker in solid state version. Even Parity Generator and Even Parity Checker play an important role in error detection. As Even Parity Generator and Even Parity Checker are now a days being used quite extensively in electronics, this Training Board has great educational value.

Practical experience on these boards carries great educative value for Science and Engineering Students.

Object

- 12 bit Even parity generator

- 13 bit Even parity checker

Features

The board consists of the following built-in parts:

- Toggle Switches : 13 nos.

- Led's : 15 (13 for input bits and 2 for output)

- ICs : 7486/3

- Adequate no. of other electronic components.

- Mains ON/OFF switch, Fuse and Jewel light.

- The unit is operative on 230V at 50Hz AC Mains.

- Strongly supported by detailed Operating Instructions, giving details of Object, Theory, Design procedures, Report Suggestions and Book References.

Technical specifications

- Data Width:

- Even Parity Generator: 12 bits

- Even Parity Checker: 13 bits

- Parity Type:

- Even Parity

- Input Interface:

- Even Parity Generator: 12-bit input data

- Even Parity Checker: 13-bit input data (12 data bits + 1 parity bit)

- Output Interface:

- Even Parity Generator: Single-bit output indicating whether the received data from 12 bits has even parity.

- Even Parity Checker: Single-bit output indicating whether the received data from 13 bits has even parity.

- Logic Operation:

- Even Parity Generator: XOR operation for generating the parity bit.

- Even Parity Checker: XOR operation for checking the parity.

- Implementation Technology:

- Digital logic gates – XOR gate and NOT Gate.

- Simplicity and Scalability:

- This design is for 12 bits only and it can be extended for 16, 32, 64, 128, 256 bits and more according to the bits size the number of Logic Gates required will also increase.

- Specification of Logic Probe:

- Operating Voltage : 5V regulated DC at 150mA , Ripple < 3mV

- Logic State Indications :

- High Level '1' : 'H' (HIGH)

- Low Level '0' : 'L'(LOW)

- Logic Families : TTL

- Frequency : Upto 50MHz for TTL

91-9829132777

91-9829132777